## GàNSafe™

#### 1. Features

- V<sub>DS</sub> 650V continuous / 800V transient

- 35 m $\Omega$  R<sub>DS(ON)</sub> MAX 25C and 58 A I<sub>DS(CONTINUOUS)</sub>

- TOLL-4L thermally-enhanced, bottom-cooled

- PWM input compatibility 10 to 20 V

- Paralleling capability up to 2x power ICs

- Zero reverse-recovery charge

- Turn-ON and Turn-OFF dV/dt programmability

- Up to 2 MHz operation

- Short Circuit Protection with 350 ns latency

- dV/dt immunity up to 100 V/ns

- 2kV ESD all Pins

- AEC-Q100 Grade 1 (ordering option)

- RoHS, Pb-free, REACH-compliant

#### 2. Applications / Topologies

- AC-DC, DC-DC, DC-AC, and ZVS, CCM

- Half-bridge, full-bridge, 3-phase, buck/boost

- Data Center CRPS, and PV Inverter/ESS

- EV OBC & DC-DC converter, and motor drive

V6515

RELIMINARY DATASHEET

## 3. Description

The NV6515 is a thermally-enhanced bottomcooled SMD version of the GaNFast<sup>™</sup> power IC family, optimized for higher power systems using GaNSafe<sup>™</sup> technology, making it the ideal choice for high-frequency, high-power-density, and highefficiency power systems in data center, solar, industrial, and automotive segments.

GaNFast power ICs integrate GaN FET(s) with gate drive to create an easy-to-use power stage building block.

GaNSafe technology further integrates critical protection and performance features that enable unprecedented reliability and robustness. The TOLL package ties this architecture together with industry-standard thermally-enhanced packaging, creating dependable solutions for world-class size/weight, efficiency, and cost.

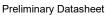

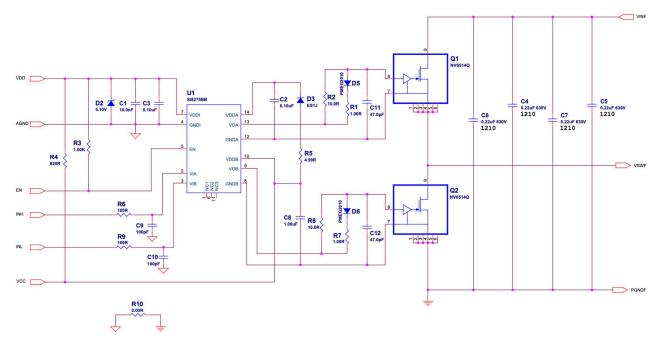

#### 4. Typical Application Circuits

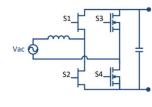

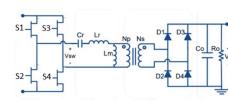

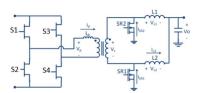

**PSFB** or DAB

**BTP PFC**

## Navitas GầNSafe™

14

## 5. Table of Contents

Electrify Our World™

| (1) <u>Features</u>                                            | pg. 1      |

|----------------------------------------------------------------|------------|

| (2) Applications / Topologies                                  | pg. 1      |

| (3) <u>Description</u>                                         | pg. 1      |

| (4) Typical application circuits                               | pg. 1      |

| (5) <u>Table of contents</u>                                   | pg. 2      |

| (6) <u>Absolute maximum ratings</u>                            | pg. 3      |

| (7) <u>Recommended operating conditions</u>                    | pg. 4      |

| (8) <u>ESD ratings</u>                                         | pg. 4      |

| (9) <u>Thermal resistance</u>                                  | pg. 4      |

| (10) Electrical characteristics                                | pg. 5      |

| (11) Inductive switching circuit diagram                       | pg. 6      |

| (12) <u>Electrical curves</u>                                  | pg. 7 – 9  |

| (13) <u>Pinout table</u>                                       | pg. 10     |

| (14) Functional description                                    | pg. 11 – 1 |

| (14.1) GaNSafe operation                                       | pg. 11     |

| (14.2) Internal gate drive power loss                          | pg. 12     |

| (14.3) Turn-ON/OFF dV/dt control                               | pg. 12     |

| (14.4) <u>Paralleling GaNSafe power ICs</u>                    | pg. 12     |

| (14.5) Short Circuit Protection                                | pg. 13     |

| (14.6) Design for V <sub>DS_CONT</sub> & V <sub>DS_TRANS</sub> | pg. 13     |

| (14.7) PCBA layout guidelines                                  | pg. 14     |

| (14.8) PCBA reference schematic                                | pg. 15     |

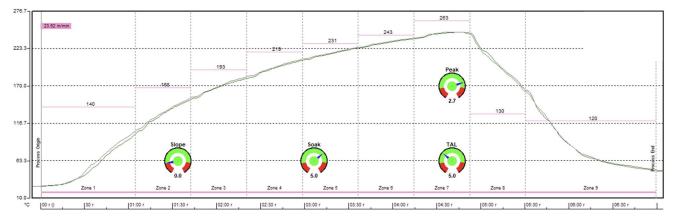

| (14.9) PCBA SMT IR reflow profile                              | pg. 15     |

| (15) Package outline dimensions                                | pg. 16     |

| (16) TnR drawing and socket orientation                        | pg. 17     |

| (17) Ordering information                                      | pg. 18     |

| (18) <u>Revision history</u>                                   | pg. 18     |

|                                                                |            |

NV6515

## 6. Absolute Maximum Ratings<sup>(Note 1)</sup> (with respect to Source, T<sub>CASE</sub> = 25°C, unless specified)

GầNSafe™

NV651

PRELIMINARY DATASHEET

.5

lavitas

Electrify Our World™

| Symbol                   | Parameter                                                                                                                                                                         | Мах         | Units |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|

| V <sub>DS(CONT)</sub>    | Continuous Drain-to-Source voltage                                                                                                                                                | -7 to +650  | V     |

| V <sub>DS(TRAN)</sub>    | Transient Drain-to-Source voltage (Note 2)                                                                                                                                        | 800         | V     |

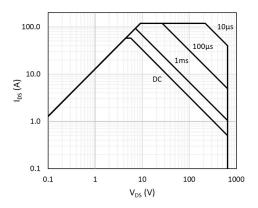

| I <sub>DS(CONT)</sub>    | Continuous Drain current (T <sub>CASE</sub> = 25 °C) <sup>(Note 3)</sup><br>Continuous Drain current (T <sub>CASE</sub> = 100 °C, T <sub>JUNC</sub> = 150 °C) <sup>(Note 3)</sup> | 58<br>43    | А     |

| I <sub>DS_PULSE</sub>    | Pulsed Drain current (10 $\mu$ s @ T <sub>JUNC</sub> = 25 °C) (Note 3)<br>Pulsed Drain current (10 $\mu$ s @ T <sub>JUNC</sub> = 150 °C) (Note 3)                                 | 119<br>43   | A     |

| V <sub>DRIVE_CONT</sub>  | Continuous input voltage measured between $V_{\mbox{\scriptsize DRIVE}}$ and SK pins                                                                                              | -0.6 to 20  | V     |

| V <sub>DRIVE_TRANS</sub> | Transient input voltage measured between $V_{\text{DRIVE}}$ and SK pins $^{(Note 4)}$                                                                                             | -2.0        | V     |

| dV/dt                    | Slew Rate on Drain-to-Source                                                                                                                                                      | 100         | V/ns  |

| T <sub>JUNC</sub>        | Junction Temperature                                                                                                                                                              | -40 to +150 | °C    |

| TSTOR                    | Storage temperature                                                                                                                                                               | -55 to +150 | °C    |

(1) Absolute Maximum Ratings are stress ratings, and subjecting devices to stresses beyond these ratings may cause permanent damage.

(2)  $V_{DS (TRAN)}$  allows for surge ratings during *non-repetitive* events that are < 100 µs.

- (3) Limited by Short Circuit Protection.

- (4) Limited to 200 ns.

## 7. Recommended Operating Conditions (Note 5)

Navitas

Electrify Our World™

| Symbol                 | Parameter                           | Min  | Тур | Мах | Units |

|------------------------|-------------------------------------|------|-----|-----|-------|

| V <sub>DRIVE_H</sub>   | Drive input pin voltage high        | 11   | 15  | 18  | V     |

| Vdrive_L               | Drive input pin voltage low         | -0.3 | 0   | 0.3 | V     |

| Rdrive_on              | Turn-ON VDRIVE Pin series resistor  | 2.2  |     | 50  | Ω     |

| R <sub>DRIVE_OFF</sub> | Turn-OFF VDRIVE Pin series resistor | 2.2  |     | 25  | Ω     |

GàNSafe™

(5) Exposure to conditions beyond maximum recommended operating conditions for extended periods of time may affect device reliability.

#### 8. ESD Ratings

| Symbol | Parameter                              | Мах   | Units |

|--------|----------------------------------------|-------|-------|

| HBM    | Human Body Model (per JS-001-2014)     | 2,000 | V     |

| CDM    | Charged Device Model (per JS-002-2014) | 1,000 | V     |

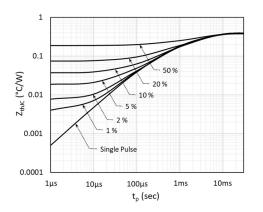

#### 9. Thermal Resistance

| Symbol                             | Parameter                           | Мах  | Units |

|------------------------------------|-------------------------------------|------|-------|

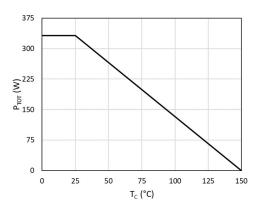

| $R_{_{\Theta_{JUNC}\text{-}CASE}}$ | Junction-to-Case Thermal Resistance | 0.38 | °C/W  |

NV6515

#### **10. Electrical Characteristics**

| Symbol                                 | unless otherwise specified: V <sub>DS</sub> <b>Parameter</b>          | Min  | Тур  | Max | Units | Conditions                                                                                                                                    |

|----------------------------------------|-----------------------------------------------------------------------|------|------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Drive Pin C                            | haracteristics                                                        |      |      | 8   | 1     | 1                                                                                                                                             |

| DRIVE_OPERATING                        | V <sub>DRIVE</sub> operating current                                  |      | 3.6  |     | mA    | $V_{DRIVE}$ = 15V, F <sub>SW</sub> = 300kHz,<br>50% D.C., V <sub>DS</sub> = 0V                                                                |

| I<br>DRIVE_LEAKAGE                     | V <sub>DRIVE</sub> leakage current                                    |      | 1.5  |     | mA    | V <sub>DRIVE</sub> = 15V                                                                                                                      |

| Switching (                            | Characteristics                                                       |      |      |     |       |                                                                                                                                               |

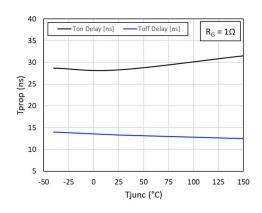

| t <sub>on</sub>                        | Turn-ON propagation delay                                             | 25   |      | 36  | ns    |                                                                                                                                               |

| t <sub>off</sub>                       | Turn-OFF propagation delay                                            | 8    |      | 17  | ns    | $ \begin{array}{l} \mbox{Fig 1,2 ; -40 } \mbox{°C} \leq \mbox{$T_{CASE}$} \leq +125 \ \mbox{°C} \\ \mbox{$R_{DRIVE}$} = 1\Omega \end{array} $ |

| t <sub>on_MIN</sub>                    | Minimum Drive on-time pulse duration                                  | 75   |      |     | ns    | $R_{DRIVE} = 1\Omega$                                                                                                                         |

| Short Circu                            | it Protection (SCP)                                                   |      |      |     |       |                                                                                                                                               |

| V_DS_SCP                               | V <sub>DS(ON)</sub> Short Circuit Detect Threshold                    | 11.5 | 13.5 |     | V     | $\begin{vmatrix} 18V \ge V_{\text{DRIVE}} \ge 11V, T_{\text{JUNC}} = -40 \text{ °C} \\ \text{to +150 °C, verified by design} \end{vmatrix}$   |

| t<br>scp_dly_turn-on                   | Delay from Short Circuit Event to Soft<br>Shut Down, into Turn-ON     |      | 350  |     | ns    | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                      |

| t                                      | Delay from Short Circuit Event to Soft<br>Shut Down, during Operation |      | 50   |     | ns    | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                      |

| GaN FET C                              | haracteristics                                                        |      |      |     |       |                                                                                                                                               |

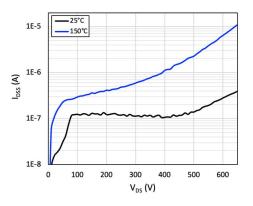

| l<br><sub>DSS</sub>                    | Drain-Source leakage current                                          |      | 1.2  |     | μA    | $V_{DS} = 650 \text{ V}, V_{DRIVE} = 0 \text{ V}$                                                                                             |

| l<br><sub>DSS</sub>                    | Drain-Source leakage current                                          |      | 118  |     | μA    | V <sub>DS</sub> = 650 V, V <sub>DRIVE</sub> = 0 V, T <sub>JUNC</sub> = 150 °C                                                                 |

| R <sub>DS(ON)</sub>                    | Drain-Source resistance                                               |      | 25   | 35  | mΩ    | V <sub>DRIVE</sub> = 15V                                                                                                                      |

| R <sub>DS(ON)</sub>                    | Drain-Source resistance                                               |      | 60   |     | mΩ    | $V_{DRIVE}$ = 15V, $T_{JUNC}$ = 150 °C                                                                                                        |

| $V_{_{\rm SD}}$                        | Source-Drain reverse voltage                                          |      | 3.3  |     | V     | $V_{DRIVE} = 0 V, I_{SD} = 22 A$                                                                                                              |

| I <sub>SD</sub>                        | Source-Drain reverse current                                          |      | 110  |     | A     | $V_{DRIVE}$ = 0V, $V_{DS}$ = 7V, 50us pulse,<br>based on $P_{DISSIPATION}$                                                                    |

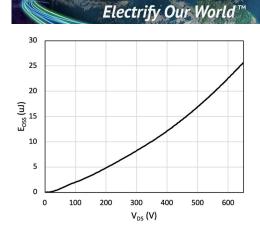

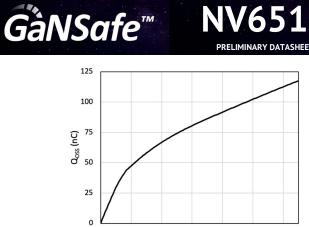

| Q <sub>oss</sub>                       | Output charge                                                         |      | 92   |     | nC    | $V_{DS} = 400 \text{ V}, V_{DRIVE} = 0 \text{ V}$                                                                                             |

| Q <sub>RR</sub>                        | Reverse recovery charge                                               |      | Zero |     | nC    |                                                                                                                                               |

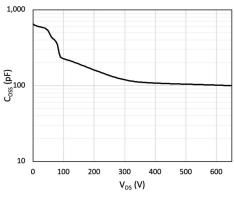

| C <sub>oss</sub>                       | Output capacitance                                                    |      | 108  |     | pF    | $V_{DS} = 400 \text{ V}, V_{DRIVE} = 0 \text{ V}$                                                                                             |

| C <sub>O(er)</sub> <sup>(Note 4)</sup> | Effective output capacitance, energy related                          |      | 152  |     | pF    | $V_{DS} = 400 \text{ V}, V_{DRIVE} = 0 \text{ V}$                                                                                             |

| C <sub>O(tr)</sub> (Note 5)            | Effective output capacitance, time related                            |      | 229  |     | pF    | $V_{DS} = 400 \text{ V}, V_{DRIVE} = 0 \text{ V}$                                                                                             |

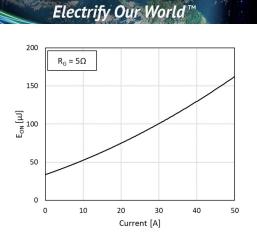

| E <sub>ON</sub>                        | Switching energy, Turn-ON                                             |      | 80   |     | μJ    | $V_{DS} = 400 \text{ V}, \text{ R}_{DRIVE} = 1\Omega$                                                                                         |

| E <sub>OFF</sub>                       | Switching energy, Turn-OFF                                            |      | 12   |     | μJ    | V <sub>DS</sub> = 0 to 400 V                                                                                                                  |

|                                        | 1                                                                     |      | 1    |     |       | 1                                                                                                                                             |

GàNSafe™

(6)  $C_{O(er)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V (7)  $C_{O(tr)}$  is a fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V

NV6515

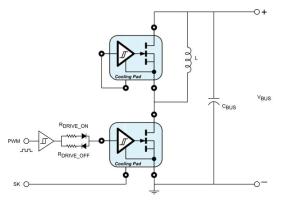

## 11. Inductive Switching Test Circuit and Typical Waveforms

Figure 1. Inductive Switching Test Circuit

Figure 2. Prop Delay, Rise/Fall Time

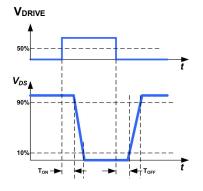

12. Electrical Curves (GaN FET, T<sub>CASE</sub> = 25 °C unless otherwise specified)

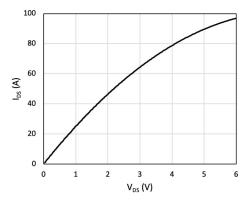

Fig. 3. I<sub>DS</sub> vs. V<sub>DS</sub>, T<sub>JUNC</sub> = 25 °C

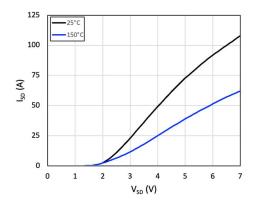

Fig. 5. I<sub>SD</sub> vs. V<sub>SD</sub>, T<sub>JUNC</sub> = 25 °C, 150 °C

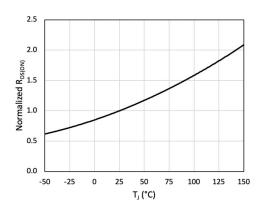

Fig. 7. Normalized R<sub>DSON</sub> vs. T<sub>JUNC</sub>

Preliminary Datasheet

Fig. 4. I<sub>DS</sub> vs. V<sub>DS</sub>, T<sub>JUNC</sub> = 150 °C

Fig. 6. I<sub>DSS</sub> vs. V<sub>DS</sub>, T<sub>JUNC</sub> = 25 °C, 150 °C

Fig. 8. Coss vs. VDS

Vavitas

Fig. 9. Eoss vs. VDs

Fig. 11. tprop\_on, off vs. Tjunc

Fig. 13. Transient Ro\_JUNC-CASE

NV651

.5

300

V<sub>DS</sub> (V)

400

500

600

200

0

100

Fig. 12. PDISSIPATION VS. TCASE

Fig. 14. Safe Operating Area, T<sub>JUNC</sub> = 25°C

Preliminary Datasheet

8

avitas

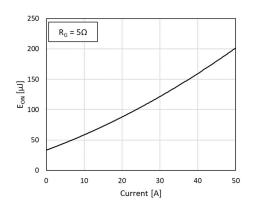

Fig. 15. Eon vs. IDS, TJUNC = 25 °C

Fig. 17. Eon vs. I<sub>DS</sub>, T<sub>JUNC</sub> = 125°C

NV651

5

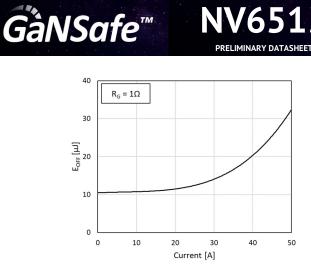

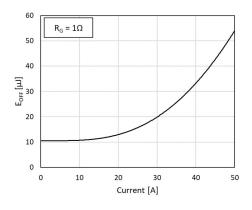

Fig. 16. E<sub>OFF</sub> vs. I<sub>DS</sub>, T<sub>JUNC</sub> = 25 °C

Fig. 18. E<sub>OFF</sub> vs. I<sub>DS</sub>, T<sub>JUNC</sub> = 125°C

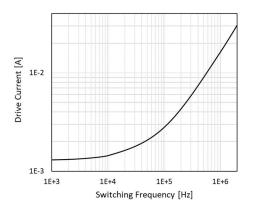

Fig. 19. I<sub>DRIVE</sub> vs. Switching Frequency (F<sub>sw</sub>)

Preliminary Datasheet

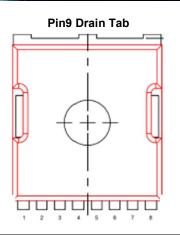

### 13. Pinout Table

Navitas

Electrify Our World™

ĜâNSɑfe™

| Pin                                  | Pin    |              | Description                                                         |  |

|--------------------------------------|--------|--------------|---------------------------------------------------------------------|--|

| Number                               | Symbol | I/O (Note 8) | Description                                                         |  |

| 1~6, Bottom Pad                      | Source | G            | Source of power FET                                                 |  |

| 7                                    | SK     | G            | Connect Driver IC between V <sub>DRIVE</sub> and SK (Kelvin return) |  |

| 8                                    | VDRIVE | I            |                                                                     |  |

| 9 (Tab)                              | Drain  | Р            | Drain of power FET                                                  |  |

| (8) G = Ground, I = Input, P = Power | •      |              |                                                                     |  |

NV6515

## 14. Functional Description

Navitas

Electrify Our World™

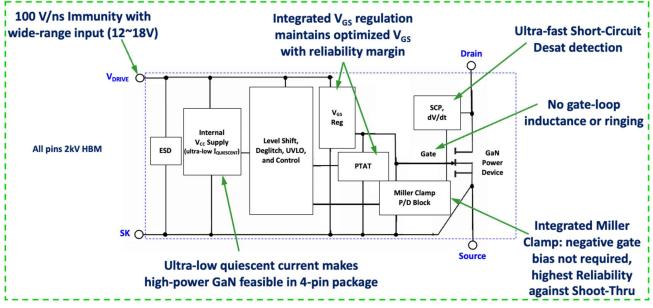

#### 14.1. GaNSafe Operation: Internal Regulated V<sub>GS</sub> and Block Diagram

GaNSafe power IC's are the industry's first GaN power devices allowing high speed operation in an industry-standard 4-Pin package (Drain / Source /  $V_{DRIVE}$  / SK) ~ *also providing regulated*  $V_{GS}$  *and protection & performance features!*

GầNSafe™

$V_{DRIVE}$  Input: In order to achieve these advanced capabilities in only 4 terminals, an isolated PWM with ≥500mA output current is required (see sect. 14.10 reference schematic). The PWM output (V<sub>DRIVE</sub> input) must be ≥10V (*absolute minimum*), however, V<sub>DRIVE</sub> voltage ≥11V is *strongly recommended*. During normal operation all the GaNSafe internal circuit blocks are active with V<sub>DRIVE</sub> > 8.5V, however, all functions (dV/dt slew rate over Temp, SCP, etc.) are only guaranteed to meet datasheet parameters with V<sub>DRIVE</sub> ≥10V (recommended ≥11V).

**Internal regulated V**<sub>GS</sub> turns-ON the GaN gate with 6.7V and OFF at 0V. Negative gate bias is NOT required since there is an internal Miller Clamp to maintain the GaN gate OFF during PWM OFF state. The internal regulated V<sub>GS</sub> has a Positive TempCo (PTC) to optimize V<sub>GS</sub> over -40C to +150C T<sub>JUNC</sub>, maintaining V<sub>GS</sub> close to optimal 6.7V but below 7.0V lifetime reliability constraint. This is part of the overall reliability and robustness provided by GaNSafe.

$V_{DS}$  Rating: During switching, the Drain toggles between Source voltage and  $V_{IN}$  (650V maximum). The Drain can withstand *non-repetitive* pulses up to 800V for <100 us [see sect. 6 for  $V_{DS(TRAN)}$  rating]. The platform design must have appropriate commutation loop decoupling and adhere to voltage margin.

**PWM IC:** A dual PWM driver can be utilized (sect. 14.10 reference schematic), or a single PWM driver with separate Turn-ON and Turn-OFF outputs can be used, such as Si8273BB with 8V UVLO.

**Minimum On-Time:** GaNSafe power ICs have an integrated 5V power supply and Level Shift & Deglitch circuits. The  $t_{ON\_MIN}$  (minimum valid on-time pulse duration at the  $V_{DRIVE}$  pin) is 75ns (sect. 10).

#### Figure 20. GaNSafe Block Diagram

Preliminary Datasheet

NV651

ELIMINARY DATASHE

# Navitas GâNSafe™ NV6515 Electrify Our World™ PRELMINARY DATASHEET

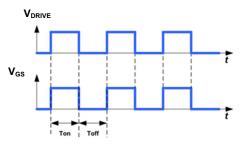

#### 14.2. Internal Gate Drive Power Loss

Internal gate drive power loss on GaNSafe power IC's can be projected by using  $I_{DRIVE}$  value from Fig. 19 ( $I_{DRIVE}$  vs.  $F_{SW}$ ), interpolated between duty cycle curves, multiplied by  $V_{DRIVE}$  (i.e.,  $I_{DRIVE} * V_{DRIVE}$ ).

Figure 21. Normal Operating Mode Timing Diagram (VDRIVE input vs. VGS)

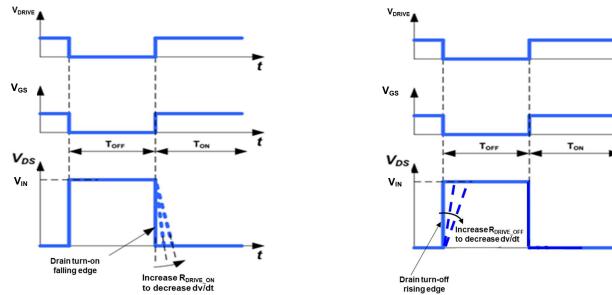

#### 14.3. Programmable Turn-ON and Turn-OFF dV/dt Control

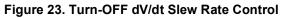

During start-up or hard-switching condition, it may be desirable to limit slew rate (dV/dt) on the Drain. To program Turn-ON slew rate connect  $R_{DRIVE_ON}$  in series with  $V_{DRIVE}$  pin (as shown in sect. 14.10 reference schematic). Conversely, Turn-OFF slew rate is programmed using  $R_{DRIVE_OFF}$  series resistor value. These resistors ( $R_{DRIVE_ON, OFF}$ ) set the *current* of the internal gate drive circuit, therefore setting dV/dt.

Figure 22. Turn-on dV/dt Slew Rate Control

#### 14.4. Paralleling GaNSafe power IC's

GaNSafe power IC's can be paralleled up to a recommended maximum of <u>Qtv2</u>, maintaining close  $T_{ON}$  and  $T_{OFF}$  matching of propagation delays. The following schematic revisions should be made:

- Add Kelvin-Source resistors in the return path from *each* SK Pin back to the external isolated PWM driver

- Adjust R<sub>DRIVE</sub> value to assist T<sub>ON</sub> / T<sub>OFF</sub> matching

t

t

#### 14.5. Short Circuit Protection

Navitas

Electrify Our World™

GaNSafe power ICs continuously monitor  $V_{DS}$  and trigger Short Circuit Protection (SCP) above  $V_{DS_SAT}$  trip point (listed in sect. 10). GaNSafe power ICs Turn-OFF via Soft Shutdown (S/D) after SCP is triggered, holding the GaN gate LOW on a cycle-by-cycle basis unless  $V_{DS_SAT}$  setpoint is CLEARED or until the system undergoes Power-ON Reset (POR).

GầNSafe™

$V_{DS\_SAT}$  Min/Max tolerances (listed in sect. 10) are designed to set SCP trip point  $\geq$ 20% higher than the GaN power device saturation current, up to 150C. SCP latency is 350ns including Blanking Time during Turn-ON *into* a short circuit event, but SCP latency is 50ns when a short circuit event occurs during normal switching operation.

It is critical for GaN devices to have integrated SCP (Short Circuit Protection) due to GaN's shorter SCWT (Short Circuit Withstand Time) and the need for ultra-low latency on SCP operation. However, OTP (Over Temp) & OCP (Over Current) are typically implemented via system DSP.

#### 14.6. Design for VDS(CONT) and VDS(TRAN)

GaNSafe power ICs have been designed and tested to provide significant design margin for continuous and transient voltage conditions, for topologies typically used in high power operation up to 22kW. These voltage levels and recommended design margin can be analyzed using Fig. 24 below. When the GaNSafe power IC is switched off, energy stored in the output circuit causes  $V_{DS}$  overshoot ( $V_{SPIKE}$ ), and after dissipation of the stored energy  $V_{DS}$  settles to the level of the bus voltage.

- For *repetitive* events, derating should be applied from V<sub>DS(TRAN)</sub> rating (800V) to V<sub>DS(CONT)</sub> rating (650V max) under the worst case operating conditions.

- It is recommended to design the system such that  $V_{DS-OFF}$  is  $\leq 520V$  (80% of  $V_{DS(CONT)}$  rating).

- Non-repetitive events are infrequent, one-time conditions such as line surge, ESD, and lightning strike. No derating from 800V is needed for non-repetitive V<sub>SPIKE</sub> durations < 100 μs.</li>

Figure 24. VDS(CONT) and VDS(TRAN)

NV651

ELIMINARY DATASH

#### 14.7. PCB Layout Guidelines

PCB layout is critical for thermal management, noise immunity, and proper operation of the power IC. The following rules should be followed carefully during the design of the PCB layout:

• Place IC filter and programming components <u>directly adjacent to the GaNSafe power IC</u>, and reference all these components to the SK pin.

GầNSafe™

- Place an 0402 site for MLCC between SK and V<sub>DRIVE</sub> Pins (<u>directly adjacent to the pins</u>). This site may be stuffed with a 100pF MLCC if additional noise immunity on V<sub>DRIVE</sub> Pin is desired.

- Observe the limits on <u>R<sub>DRIVE ON</sub> and R<sub>DRIVE OFF</sub> minimum values</u> in ROC Sect. 7.

- Do not run power SOURCE currents through SK pin!

- For best thermal management, place thermal vias in the source pad area to conduct the heat out through the bottom of the package and through the PCB board to other layers.

- Use large PCB thermal planes (connected with thermal vias to the source pad) and additional PCB layers to reduce IC temperatures as much as possible.

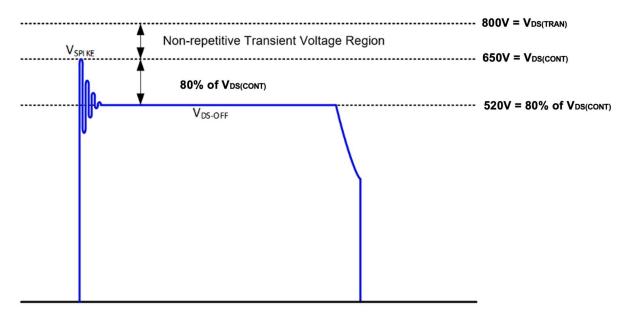

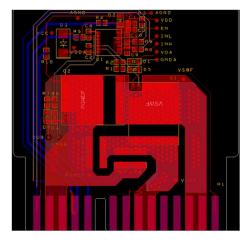

Pictorials below shows a typical Half-Bridge layout from a THMT Eval Board, and PCBA Footprint.

NV651

#### 14.8. Reference Schematic

GầNSafe™

#### 14.9. PCBA SMT IR Oven Profile (guideline only):

Navitas

Electrify Our World™

NV6515

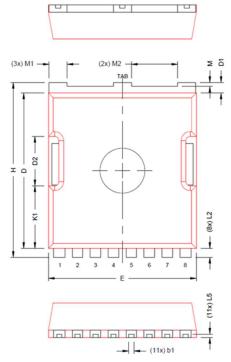

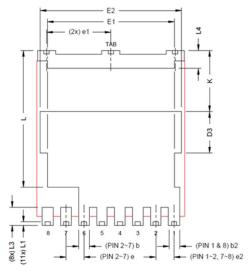

#### 15. Package Outline Dimensions:

Navitas

Electrify Our World™

GàNSafe™

NV6515

PRELIMINARY DATASHEET

- DIMENSIONING AND TOLERANCING CONFORME TO ASME Y14.5M 1994,

ALL DIMENSIONS ARE IN MILLIMETERS. ANOLES ARE IN DEGREES.

MAXIMUM ALLOWABLE BURRS IS 0.076 MM IN ALL DIRECTIONS.

COPLANARITY ZONE APPLIES TO THE EXPOSED HEAT SLUG AS WELL AS THE TERMINALS.

| SYM | MIN   | NOM       | MAX   |

|-----|-------|-----------|-------|

| A   | 2.15  | 2.30      | 2.45  |

| b   | 0.70  | 0.70      | 0.80  |

| b1  | _     | 0.35 REF. | -     |

| b2  | 0.75  | 0.75      | 0.85  |

| с   | 0.40  | 0.50      | 0.60  |

| D   | 10.18 | 10.38     | 10.58 |

| D1  | 0.50  | 0.70      | 0.90  |

| D2  | _     | 3.30 REF. | _     |

| D3  | -     | 2.77 REF. | _     |

| E   | 9.70  | 9.90      | 10.10 |

| E1  | -     | 8.50 REF  | -     |

| E2  | —     | 9.46 REF. | -     |

| e   | 1.15  | 1.20      | 1.25  |

| e1  | 4.20  | 4.30      | 4.40  |

| e2  | 1.175 | 1.225     | 1.275 |

| н   | 11.48 | 11.68     | 11.88 |

| к   | -     | 4.08 REF. | _     |

| K1  | -     | 4.17 REF. | -     |

| L   | -     | 9.13 REF. | -     |

| L1  | -     | 0.23 REF. | _     |

| L2  | 0.50  | 0.60      | 0.70  |

| L3  | 1.10  | 1.20      | 1.30  |

| L4  | 1.10  | 1.20      | 1.30  |

| L5  | -     | 0.23 REF. | -     |

| M   | 0.16  | 0.26      | 0.36  |

| M1  | 1.10  | 1.20      | 1.30  |

| M2  | 3.00  | 3.10      | 3.20  |

| Ø   | 8*    | 10*       | 12*   |

Preliminary Datasheet

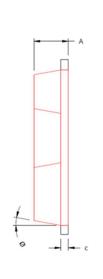

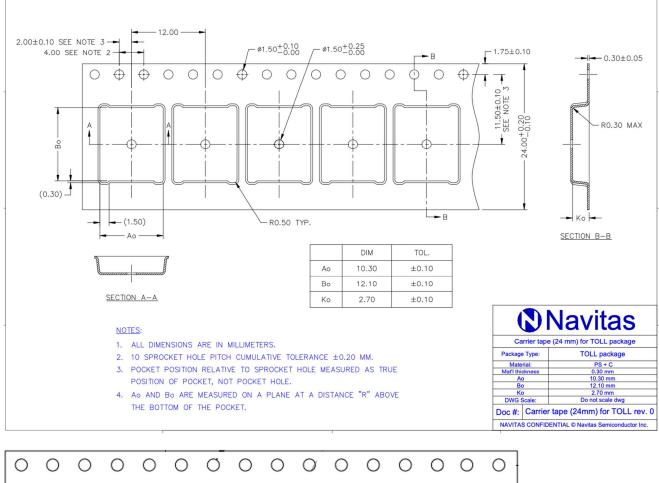

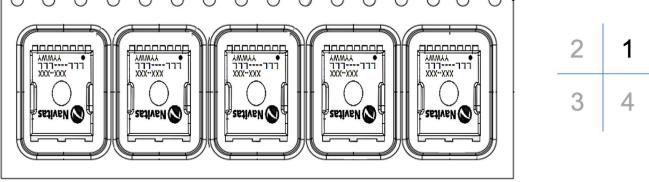

16. TnR Drawing and Socket Orientation

Electrify Our World™

Navitas GàNSafe™

NV6515

#### 17. Ordering Information

Navitas

Electrify Our World™

| Part Number | Qualification     | Package           | MSL Rating | TnR Sizes/Qtys              |  |  |

|-------------|-------------------|-------------------|------------|-----------------------------|--|--|

| NV6515      | JEDEC             |                   |            | Standard (13" dia) Qty1,500 |  |  |

| NV6515-MR   | JEDEC             | TOLL-4L           | 2          | Mini-Reel (7" dia) Qty340   |  |  |

| NV6515Q     | AEC-Q100 Grade 1  | Bottom-cooled SMD | 3          | Standard (13" dia) Qty1,500 |  |  |

| NV6515Q-MR  | -40 °C to +125 °C |                   |            | Mini-Reel (7" dia) Qty340   |  |  |

GầNSafe™

#### 18. Revision History

| Date                                                          | Status              | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Oct 20 <sup>th</sup> , 2022                                   | Initial Publication | Preliminary Datasheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Feb 1 <sup>st</sup> , 2023 and<br>Apr 20 <sup>th</sup> , 2023 | Revisions           | <ul><li>Updated electrical characteristics table</li><li>Added reference schematic</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Oct 6 <sup>th</sup> , 2023                                    | Revision            | <ul> <li>Absolute Maximum Ratings: V<sub>DRIVE_TRANS</sub> (transient)</li> <li>ROC table: Turn-ON/OFF R<sub>DRIVE</sub> series resistor values</li> <li>Electrical Characteristics table: toN/OFF and t<sub>PROP_DELAY</sub> Min/Max values with Test Conditions ; I<sub>SD</sub> Typ value ; SCP parameters V<sub>DS_SCP</sub> trip point and delay times ; (all) Switching Parameters</li> <li>Electrical curves (all) updated from FT Characterization data</li> <li>Applications: 14.3 updated ; 14.6 added ; 14.7 &amp; 14.8 updated</li> <li>TnR DWG and Socket Orientation DWG added</li> </ul> |  |  |  |

| Jan 12 <sup>th</sup> , 2024                                   | Revision            | <ul> <li>Electrical Characteristics table: VDRIVE_OPERATING, VDRIVE_LEAKAGE,<br/>ton/off, VDs_scp, IDss_25°c, IDss_150°c, Vsd, Isd_PULsed, Co(TR), EON/OFF</li> <li>Updated Figures 11 – 19</li> <li>Added Sect. 14.6</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

NV6515

PRELIMINARY DATASHEET

#### **Additional Information**

DISCLAIMER Navitas Semiconductor Inc. (Navitas) reserves the right to modify the products and/or specifications described herein at any time and at Navitas' sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied. This document is presented only as a guide and does not convey any license under intellectual property rights of Navitas or any third parties.

Navitas' products are not intended for use in applications involving extreme environmental conditions or in life support systems. Navitas' products are not intended for use in automotive **safety** systems. Products supplied under Navitas Standard <u>Terms and Conditions</u> for Sale.

Navitas Semiconductor, Navitas, GaNFast™, GaNSafe™, and associated logos are registered trademarks of Navitas. Navitas Semiconductor Ltd., 22 Fitzwilliam Square South, Saint Peter's, Dublin, D02 FH68, Republic of Ireland Copyright ©2024 Navitas Semiconductor Inc. All rights reserved.

Preliminary Datasheet